## MEMS-BASED STORAGE DEVICES

## Integration in Energy-Constrained Mobile Systems

In the digital era, the amount of data a person stores has multiplied significantly. The growth for storage capacity is increasing by about 30% - 60% per year. People keep track of their personal data for every event in their life, while new regulations stipulate storing business information for long periods of time.

This dissertation puts in the hands of the reader a four-dimensional investigation of a new class of storage devices, called MEMS-based storage devices. The research reported on enhances the energy-efficiency, reduces the cost, increases the performance, and extends the lifetime of this class of devices.

An emperical comparison to Flash memory is carried out in the frame of mobile battery-powered devices. Optimization results support the big potential promised by MEMS-based storage devices, demonstrating their ability to take off in the storage-demanding energy-aware digital era.

Mohammed G. Khatib received his Master's degree in Computer Science from the Technical University of Braunschweig in 2004, where he worked as a researcher from 2002 through 2004. He visited the Storage Systems Research Center of the University of California at Santa Cruz in Spring of 2008.

Mohammed received several awards of academic excellence, and received a number of travel grants. His research interests include computer architecture and storage systems.

Cover desing by the author Cover picture courtesy from IBM Research Laboratories, Zurich Mohammed G. Khatib

ISBN: 978-90-365-2847-4

MEMS-BASED STORAGE

DEVICES

## MEMS-BASED STORAGE DEVICES

## Integration in Energy-Constrained Mobile Systems

Mohammed G. Khatib

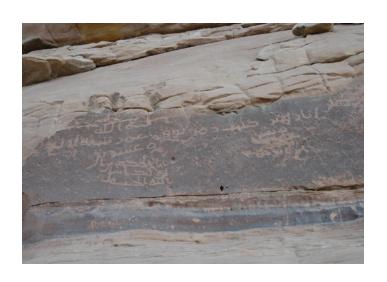

The opening-page photograph shows the earliest dated Islamic inscription written in Arabic in the Hijazi script. It dates back to the 24 AH (644 CE). The remarkable characteristic is the presence of dotted consonants, which was not the case in the older scripts. The inscription examples the existence of data recording for a very long time. The inscription translates from top to bottom as follows: In the name of God, I, Zuhayr, wrote [this] at the time 'Umar died in the year four, and twenty (i.e., 24 AH). The photo is adopted from the Discovery Channel at http://dsc.discovery.com/news/2008/11/18/islamic-inscription.html. More information can be obtained at http://www.islamic-awareness.org/History/Islam/Inscriptions/kuficsaud.html

### MEMS-Based Storage Devices

Integration in Energy-Constrained Mobile Systems

Dissertation

#### Members of the graduation committee:

| Prof. dr.     | P. H. Hartel        | University of Twente (promoter)                |

|---------------|---------------------|------------------------------------------------|

| Dr. ir.       | L. Abelmann         | University of Twente (co-promoter)             |

| Dr.           | E. S. Eleftheriou   | IBM Research Laboratories, Zurich, Switzerland |

| Dr.           | G. W. R. Leibbrandt | NXP Research Laboratories, Eindhoven           |

| Prof. dr. ir. | S. B. Luitjens      | Philips Research Laboratories, Eindhoven       |

| Prof. dr.     | E. L. Miller        | University of California at Santa Cruz, USA    |

| Prof. dr.     | S. J. Mullender     | Alcatel-Lucent Research Laboratories, Belgium  |

| Prof. dr. ir. | G. J. M. Smit       | University of Twente                           |

| Prof. dr. ir. | A. J. Mouthaan      | University of Twente (chairman and secretary)  |

The research in this dissertation was supported by the Technology Foundation STW, applied science division of NWO and the technology programme of the Ministry of Economic Affairs under project number TES.06369.

Computer Architecture for Embedded Systems group

Distributed and Embedded Security group

The Faculty of Electrical Engineering,

Mathematics and Computer Science

P. O. Box 217

7500 AE Enschede

The Netherlands

ISSN: 1381-3617, CTIT Ph.D.-thesis series No. 09-145 Centre for Telematics and Information Technology P.O.Box 217 7500 AE Enschede The Netherlands

IPA Ph.D.-thesis series No. 2009-12 The work in this thesis has been carried out under the auspices of the research school IPA (Institute for Programming research and Algorithmics).

Copyright @ 2009 by Mohammed G. Khatib, Enschede, The Netherlands. The thesis was printed by Wöhrmann Print Service, Zutphen, The Netherlands.

All rights reserved. No part of this book may be reproduced or transmitted, in any form or by any means, electronic or mechanical, including photocopying, microfilming, and recording, or by any information storage or retrieval system, without the prior written permission of the author.

ISBN 978-90-365-2847-4 DOI 10.3990./1.9789036528474

## MEMS-BASED STORAGE DEVICES INTEGRATION IN ENERGY-CONSTRAINED MOBILE SYSTEMS

to obtain

the degree of doctor at the University of Twente,

on the authority of the rector magnificus,

prof. dr. H. Brinksma,

on account of the decision of the graduation committee,

to be publicly defended

on Thursday, June 11, 2009 at 13:15 hrs

by

Mohammed Ghiath Khatib

born on 4 June 1979, in Aleppo, Syrian Arab Republic

#### The dissertation is approved by:

Prof. dr. P. H. Hartel University of Twente (promoter)

Dr. ir. L. Abelmann University of Twente (co-promoter)

#### **ABSTRACT**

The digital era in which we are living today requires our increasing awareness of energy efficiency to reduce the negative effects on our lovely environment. We, people, are increasingly dealing with digital contents to facilitate our deals, which increases the demand for larger storage capacities than ever before.

The environmental considerations and the data explosion worldwide are calling for green and ultrahigh-density storage technologies. A storage technology, based on Micro-Electro-Mechanical Systems (MEMS), promises to deliver green and high-capacity storage systems. Storage densities up to 4 Tb/in² have already been demonstrated. With such a technology, a storage device with a capacity of 1 Tb can be mounted in a package smaller than a thumbnail, dissipating one Watt of power.

Disruptive technologies take, however, a significant amount of time to materialize into commercial products. One key reason for this delay is the difficulty of integrating and adopting new technologies. Integration, in a broad sense, involves the investigation of roles a new technology can play, and solutions to its impediments. Early solutions to the integration problem help to reduce the time to market, and most likely contribute to the success of the technology.

Flash memory, for instance, was invented in the eighties. The large demand for Flash in mobile systems has drawn the attention of researchers to investigate Flash. Just recently, researchers started looking into ways to construct storage systems based on Flash that are reliable, have low latency, and consume little energy. Flash memory has not found its way to enterprise storage yet, whereas their kin, hard disk drives, are sitting there wasting a significant amount of energy. That kind of late response to Flash is costing data centers millions of dollars every day in energy and cooling cost.

We would like to avoid such a late response for MEMS-based storage devices by being proactive in how we can get this family of devices successfully integrated as early as possible. Like any other technology, MEMS-based storage demands optimization, and has challenges that need to be tackled. In this work, we optimize MEMS-based storage, tailor it to mobile battery-powered systems, and compare it to Flash memory and Hybrid (Disk–Flash) storage.

The research of this dissertation looks mainly into the energy and cost aspects of MEMS-based storage with the following two contributions. We devise policies to reduce the energy consumption of MEMS-based storage devices. We also propose to exploit knowledge of the expected workload in configuring the data layout of a MEMS-based storage device in order to increase the effective capacity. Both contributions target at satisfying the increasing demand for green and inexpensive storage devices.

In addition to the energy and cost aspects, we make sure that the response time and the lifetime of MEMS-based storage devices are competitive. The data-layout and energy-saving policies account for the timing performance by looking at configurations that do not compromise on the response time. With respect to lifetime, we devise probe wear-leveling policies that increase the lifetime of MEMS-based storage devices with minimal influence on the energy consumption and the response time.

The dissertation incorporates the conclusions from the study of the policies, and investigates the employment of MEMS-based storage devices in important types of mobile application. For predominately streaming applications, we also investigate the influence of buffering on the energy consumption, response time, and capacity of MEMS-based storage devices. We put the technology into perspective by comparing it to Flash memory and Hybrid (Disk–Flash) storage.

Our system-level research in this dissertation identifies potential points of enhancement of MEMS-based storage devices. Enhancements are targeted at reducing the energy consumption, decreasing the response time, cutting down the per-bit cost, and increasing the lifetime of the device. Most importantly, we show that the per-bit cost of MEMS-based storage is crucial to its success. Our system-level contributes to reduce the cost, while reduction on the device level is still needed.

We provide methods and means to configure MEMS-based storage devices to prepare them to serve in different environments as a viable storage technology. Following our research findings, designers can craft storage systems based on MEMS-based storage that are reliable, energy and performance efficient, and cost effective.

#### **SAMENVATTING**

Het digitale tijdperk waarin we leven eist een toenemende bewustwording van ons energieverbruik om de negatieve effecten daarvan op onze dierbare planeet te reduceren. Wij mensen organiseren ons doen en laten steeds meer met digitale middelen, wat de benodigde opslagcapaciteit meer dan ooit vergroot.

De bewustwording van milieueffecten en de wereldwijde dataexplosie vragen om een groene opslagtechnologie met extreem hoge datadichtheden. Een veelbelovende opslagtechnologie met deze eigenschappen maakt gebruik van MEMS (Micro-Electro-Mechanical Systems). Opslagdichtheden tot  $4\,\mathrm{Tb/in^2}$  zijn al aangetoond in het laboratorium. Met deze technologie wordt het mogelijk een opslagapparaat te maken ter grootte van een vingernagel met een capaciteit van  $1\,\mathrm{Tb}$  en met een vermogensdissipatie van slechts één Watt.

Radicaal vernieuwende technologie vergt echter een behoorlijke tijd en inspanning voordat ze geschikt is voor toepassing in consumentenproducten. Een belangrijke oorzaak van deze vertraging is de moeizame integratie en acceptatie van nieuwe technologie. Breedgedragen integratie omvat onder meer onderzoek naar de plaats die de nieuwe technologie tussen bestaande technologieën kan innemen en het vinden van oplossingen voor de problemen die daarbij onvermijdelijk optreden. Vroege oplossingen voor het integratieprobleem bekorten de benodigde tijd tot de introductie op de markt en dragen hoogstwaarschijnlijk bij aan het algemeen succes van de nieuwe technologie.

Ter illustratie, Flash werd voor het eerst getoond in de jaren tachtig van de vorige eeuw. De enorme vraag naar Flash voor mobiele systemen stimuleert nu pas een enorme hoeveelheid aan onderzoek naar Flash. Zo wordt er pas recentelijk constructief onderzocht hoe men op basis van Flash-technologie betrouwbare, snelle, en energiezuinige opslagsystemen kan ontwerpen. Flash wordt nog weinig toegepast in de huidige generatie productiesystemen voor opslag, terwijl de alom toegepaste concurrent, de harde schijf, ondertussen onnodig veel energie verbruikt. Al met al kost de late reactie op de integratieproblemen met Flash dagelijks miljoenen euro's aan energie en koeling in datacentra.

Ter voorkoming van dergelijke late reacties voor MEMS-opslagapparatuur onderzoeken wij proactief hoe MEMS-apparatuur zo vroeg mogelijk kan worden geïntegreerd. MEMS-opslagapparatuur heeft, net als elke nieuwe technologie, haar eigen uitdagingen en optimalisatieproblemen. In ons onderzoek optimaliseren we het MEMS-opslagsysteem voor toepassing in mobiele, batterij-gevoede, systemen. Vervolgens vergelijken we onze resultaten met Flash-geheugen en met een hybride opslagsysteem, waarin we Flash combineren met een harde schijf.

Deze dissertatie concentreert zich op de energie- en kostenaspecten van MEMS-opslagsystemen. Onze belangrijkste bijdrages zijn methodes om het energieverbuik van dergelijke systemen te beperken. Voorts maken we bij het configureren van MEMS-opslagsystemen handig gebruik van voorkennis van de verwachte belasting, opdat de beschikbare capaciteit efficiënt wordt benut. Onze resultaten dragen bij aan de toenemende vraag naar groene opslagsystemen met extreem hoge datadichtheid. Bovendien beperken we de kosten, hetgeen acceptatie in de markt ten goede komt.

Naast de energie- en kostenaspecten zorgen we ervoor dat de reactietijd en de levensduur van MEMS-opslagsystemen kan concurreren met die van andere systemen. Onze data-layout en energiebesparingsmethodes hebben een gunstige invloed op de snelheidsprestaties; wij kijken expliciet naar configuraties die geen concessies doen aan de reactietijd. Wat betreft de levensduur van MEMS-opslagsystemen ontwikkelen we een methode voor wear-leveling<sup>1</sup> die de levensduur verlengt en tegelijkertijd het energieverbruik en de reactietijd slechts minimaal toe laat nemen.

Deze dissertatie bouwt voort op de conclusies van het onderzoek naar operationele methodes van MEMS-opslagsystemen en ze onderzoekt de praktische toepassing ervan voor enkele belangrijke mobiele toepassingen. Voor toepassingen met voornamelijk streaming data, zoals een videocamera, onderzoeken we onder andere de invloed van bufferen op het energieverbruik, de reactietijd, en de capaciteit van MEMS-opslagsystemen. We plaatsen de praktische betekenis van MEMS-opslagsystemen in perspectief door ze te vergelijken met Flash-geheugen en het eerder genoemde hybride opslagsysteem.

Ons onderzoek levert een aantal praktische aanbevelingen op voor MEMS-opslagsystemen. De aanbevelingen in deze dissertatie beogen een vermindering van het energieverbruik, een verkorting van de reactietijd, een verlaging van de kosten per bit en een verlenging van de levensduur van het systeem. Bovenal laten we zien dat de kosten per bit de cruciale factor zijn voor het succes van MEMS-opslagsystemen. Ons onderzoek draagt bij aan de kostenreductie op systeemniveau; dit laat onverlet een kostenreductie op componentniveau

Deze dissertatie presenteert methoden en middelen voor de configuratie van MEMS-opslagsystemen, waarmee deze een levensvatbaar alternatief vormen als opslagsysteem in verschillende omgevingen. Met onze onderzoeksresultaten kunnen ontwikkelaars praktische MEMS-opslagsystemen bouwen die én betrouwbaar, én energiezuinig, én snel, én betaalbaar zijn.

<sup>&</sup>lt;sup>1</sup>slijtagevereffening

#### **ACKNOWLEDGEMENTS**

Well, that is the end of an establishment period of my career, and I am still alive! Through this period I have experienced a lot on many accounts. Luckily, I was not alone during this period, but there were so many fantastic people that I worked with and met from all around the world. Had not it been for pursuing the PhD degree at Twente, I would not have got the opportunity to meet them.

The first person to meet is the person who accepted me to pursue PhD under his supervision, Pieter. You believed in me from the very first moment, and offered me the opportunity to carry out research in one of my beloved topics in Computer Science. Pieter, the unique of you is that you are an open person, easy going, and most importantly, that you let your students rule their own to prove themselves, while providing them with everything they need. I learned a lot from you, particularly the way to organize thoughts and to do research.

Hylke, you are, as I always describe you, an open, cheerful, honest, and faithful colleague. I always liked working and exchanging ideas with you. I absolutely learned from you, particularly how to frame my work for easy and effective communication, my innocent reader! I owe you getting the material of this thesis presented as they are now. I am also very privileged to have the chance to share office with you; I really had a nice time discussing with you technical and non-technical topics.

Gerard, thanks for your involvement in my work and for your comments on my thesis draft, which were very helpful. I also thank you a lot for teaming me up with the CAES group. I have had inspiring colleagues there.

I would like to thank Leon from Electrical Engineering, who gave the effort and time to review the thesis thoroughly. Your comments have improved its readability for people outside the field of computer science.

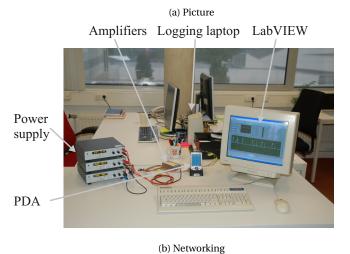

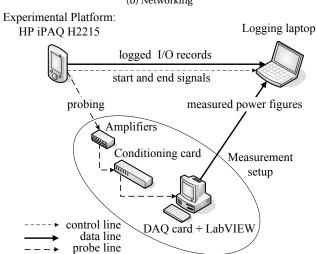

Berend-Jan, you are a nice colleague with whom I spend three years of my PhD. I benefited a lot from your review of my early papers. Frank, you have fantastic tweaking hands that helped me setting up the networking of the experimental setup. A lot of credit goes to you getting the network running properly. Johan, although we are two years out of phase, we still managed to get our PhD project moving properly with tangible results. Getting the modeling

in this thesis right would have been a tough endeavor without you, thanks a lot. Pascal, thank you for providing me with a Lagrange ground to build on and get the thesis in this nice outlook, I think.

I thank Haris Pozidis and Evangelos Eleftheriou from IBM Research Laboratories in Zurich for providing me with insights into MEMS-based storage, and answering my questions that helped shaping up the work. Also, I thank Charlotte Bolliger for her efforts to get me a high-quality picture to put on the cover of this thesis.

Steven Luitjens provided me with the measurement setup, which was an intrinsic part to carry out the experiments that are at the heart of this thesis. Thank you a lot for providing that and for hosting me for two weeks in your laboratory to get me into the setup.

During the course of my PhD I visited the University of California at Santa Cruz in the USA. Ethan accepted to work together on a research idea on MEMS and hosted me in the SSRC laboratory for a few months. That was undoubtedly a turning point for me. Ethan, your door was always open, and you were very supportive, I owe you a lot. I also wish to thank Darrell for being open and giving me from his time to answer some of my curious questions.

I would like to thank the user-committee members of my PhD project for their fruitful and useful feedback on my work through the project meetings we had.

Also, the comments I received from my graduation committee were very helpful to yet improve the quality of the thesis, thank you very much.

Many brilliant and mellow colleagues and friends were around me. Ayse, Delia, Ileana, Kavitha, Nirvana, Ozlem, Raluca, Vasughi, Albert, Jan, Michel, Mihai, Mohsen, Pierre, Philip, Supriyo, Trajce, and Qiang, thank you very much for the nice time and discussions we had together. Also the colleagues in DIES, CAES, PS, and TST-SMI groups were always there to give at least their supporting smile.

My colleagues and friends in Santa Cruz were so impressive and helpful. We could in a few weeks hang out, chat, and laugh. Andrew, Kevin, Mark, Rosie, Sasha, and Stefani thanks for being so nice colleagues and for getting me into playing Wii;-).

I do not forget my brothers and sisters in the UT-Moslem community. Ziad, Mohammed Alhaj Ali, Mohammed Jaddallah, Ahamd, Wael, Ashraf, Abdulsalam, Dlovan, Rabah, Sameh, Muhammad Asif, Khurshid, Wissam, Muhammad Kamel, and many other. Thank you all for being nice friends. I thank Hajj Omar Elamad and his wife, Hajja Basma Alshourafa, for their hospitality and for their care for the community. I thank Hadi Tabaa for showing me how adding fun to everything turns it marvelous.

I thank my friends across the boarders in Germany who kept in touch with me to preserve the minimum of the nice time we had during our Master's program, Jihad, Mustafa, Yaser Daboul, Yaser Houri, Amjad, Lars, Bachar, Nizar, Meraa, Marwan, Talal, Younes, Momtez, Khaled, Obaida, and many others. I

also thank Wael Adi for his support whenever we spoke to each other. I would like to thank Said Krayem and Safa for their nice supporting emails.

Although during the course of my stay in the USA I was spending most of the time in Santa Cruz, I managed to climb the hill to meet amazing and inspiring personalities. In a very short time, we were talking the same language, laughing, and enjoying our company. The first and the foremost is Dian. You are just an amazing women and a productive sister that I am proud of and take honor in considering you as my elder sister. I am wordless to thank you and thank your husband, Ashraf, for your care and amazing devotion. Another fantastic couple is Houda and Isa. Wow, you guys are amazing, cheerful, and outgoing. I do not forget our discussions, so fruitful. I spend most of the time when I was in San José, with my friend and brother, Danny. Every time we hang out, he was prepared to pose on me some questions that required my explanations. Sometimes I filled the gap when no questions existed. Till the moment, I wonder whether you liked one of my eloquent explanations:-).

Gratitudes go to our fantastic secretaries, Marlous, Nicole, Nienke, and Thlema. Thanks a lot for helping and for bringing a nice atmosphere in the group(s). Nienke, you revolutionized the DIES group with your help, smile, and lovely surprises. The "Appeltaart" you make is unmatched!

My family in Syria was supporting me throughout every moment of the PhD. Every year I went Syria to visit them they received me with a big and warm smile, while noticing there was a laptop in my suitcase to work on even during vacation. They kept on supporting and stuffing me with all kind of delicious food. My mother was preparing a nutritious program dedicated for me. I was taking a new cooking every day to compensate for the loss in weight and depravity of nice food, for which I was lacking experience to prepare. My father was always checking how I am doing through the PhD course and kept encouraging me until the last moment. My brothers Basem and Safouan would always snap the chance of my presence in Syria to find out more about what I am doing for PhD and to pose very interesting questions to satisfy their curiosity. Laila, my only beloved sister, she also took a considerable part into my mother's program to improve my conditions:-). I also do not forget your funny emails that brought my soul back to Syria for some moments to remember the nice times. You all are a part of this achievement. Had not it be for your support, I would not have managed through the past few years.

To the memory of my grandmother, Aliya, I love you! You left us four years ago, but you are still living in my heart. You were always supporting me and proud of me. I never doubted that I am your seventh son.

Thank you all, Mohammed G. Khatib

#### TABLE OF CONTENTS

| Table of Contents ix |      |              |                                      |    |  |

|----------------------|------|--------------|--------------------------------------|----|--|

| 1                    | Intr | Introduction |                                      |    |  |

|                      | 1.1  | Green        | and High-Density Storage             | 1  |  |

|                      |      | 1.1.1        | Current Storage Technologies         | 2  |  |

|                      |      | 1.1.2        | MEMS-Based Storage Technology        | 3  |  |

|                      |      | 1.1.3        | Requirements for MEMS-Based Storage  | 4  |  |

|                      | 1.2  | Resear       | rch Statement: The Early Integration | 5  |  |

|                      | 1.3  |              | 4 Project                            | 6  |  |

|                      | 1.4  |              | ibutions                             | 6  |  |

|                      | 1.5  | Organ        | ization of the Thesis                | 9  |  |

| 2                    | Bac  | kgroun       | d and Related Work                   | 11 |  |

|                      | 2.1  | MEMS         | S-Based Storage                      | 11 |  |

|                      |      | 2.1.1        | Enabling Technologies                | 11 |  |

|                      |      | 2.1.2        | Designs                              | 13 |  |

|                      |      | 2.1.3        | Architecture                         | 16 |  |

|                      |      | 2.1.4        | Characteristics                      | 17 |  |

|                      | 2.2  | Comp         | lementary Storage Technologies       | 19 |  |

|                      |      | 2.2.1        | Flash Memory                         | 19 |  |

|                      |      | 2.2.2        | Phase-Change Memory                  | 22 |  |

|                      | 2.3  | Relate       | d Work                               | 22 |  |

|                      |      | 2.3.1        | Modeling                             | 23 |  |

|                      |      | 2.3.2        | Design                               | 24 |  |

|                      |      | 2.3.3        | Enhancement                          | 25 |  |

|                      |      | 2.3.4        | Deployment                           | 27 |  |

|                      | 2.4  | Summ         | nary                                 | 28 |  |

| 3                    | Rese | earch M      | ethodology                           | 29 |  |

|                      | 3.1  | Experi       | iment setup                          | 29 |  |

|                      |      | 3.1.1        | The Experimental Platform            | 31 |  |

|                      |      | 3.1.2        | The Measurement Setup                | 32 |  |

|                      | 3.2  | Model        | ling MEMS-Based Storage              | 33 |  |

|   |     | 3.2.1    | Model Parameters                  | 35 |

|---|-----|----------|-----------------------------------|----|

|   |     | 3.2.2    | Timing Performance Model          | 35 |

|   |     | 3.2.3    | Energy Model                      | 36 |

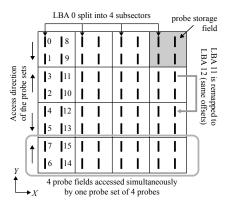

|   |     | 3.2.4    | Data Layout                       | 39 |

|   | 3.3 | Workle   | oads                              | 43 |

|   |     | 3.3.1    | Tracing Methodology               | 43 |

|   |     | 3.3.2    | Traces                            | 43 |

|   | 3.4 | Summ     | nary                              | 45 |

| 4 | Enh | anceme   | ent Policies                      | 47 |

|   | 4.1 | Opera    | tion Modes                        | 47 |

|   |     | 4.1.1    | Contrasting with Hard Disk Drives | 48 |

|   |     | 4.1.2    | Power State Machine               | 50 |

|   |     | 4.1.3    | Organization                      | 51 |

|   | 4.2 | Power    | Management Policy                 | 52 |

|   |     | 4.2.1    | Fixed-Timeout Power Management    | 52 |

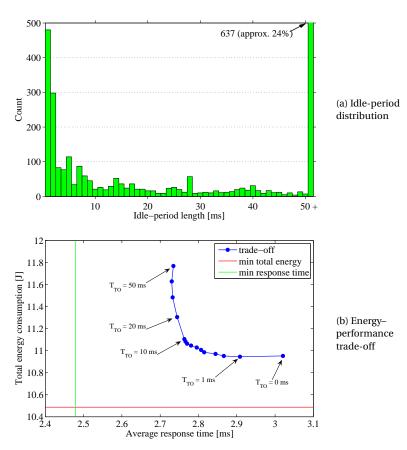

|   |     | 4.2.2    | Experimental Methodology          | 53 |

|   |     | 4.2.3    | Simulation Results                | 54 |

|   | 4.3 | Shutd    | own Policy                        | 57 |

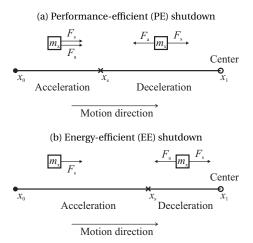

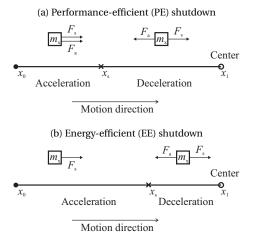

|   |     | 4.3.1    | Two Shutdown Policies             | 58 |

|   |     | 4.3.2    | Analytical Study                  | 59 |

|   |     | 4.3.3    | Trace-Based Study                 | 62 |

|   | 4.4 | Data-l   | Layout Policy                     | 63 |

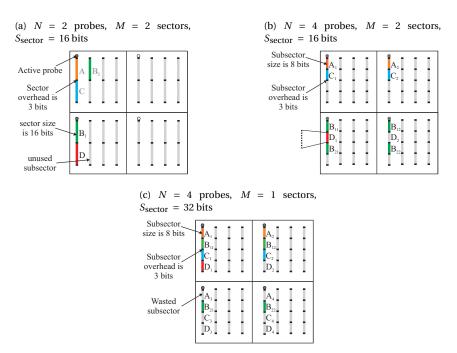

|   |     | 4.4.1    | Three Data-Layout Parameters      | 64 |

|   |     | 4.4.2    | The Physical Subsector            | 64 |

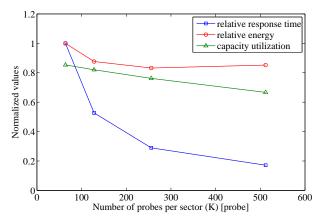

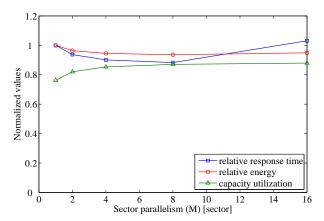

|   |     | 4.4.3    | Influence of Each Parameter       | 66 |

|   |     | 4.4.4    | Design Space                      | 72 |

|   | 4.5 | Summ     | nary                              | 74 |

| 5 | Wea | r-Leveli | ing Policies                      | 75 |

|   | 5.1 | Wear i   | in MEMS-Based Storage             | 75 |

|   |     | 5.1.1    | Types and Causes of Wear          | 75 |

|   |     | 5.1.2    | Uneven Wear and its Effects       | 77 |

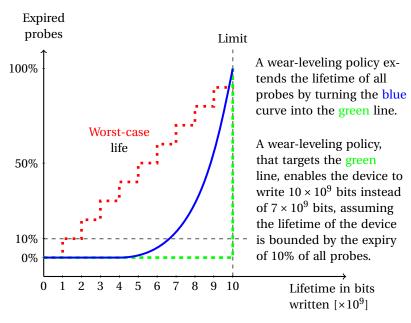

|   |     | 5.1.3    | Device Life                       | 78 |

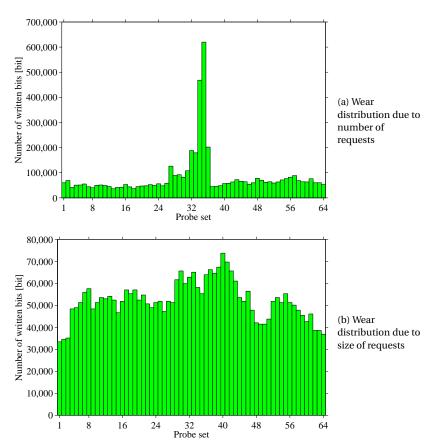

|   |     | 5.1.4    | Uneven Wear and Parallelism       | 80 |

|   | 5.2 | Cause    | s of Uneven Wear                  | 81 |

|   | 5.3 | Metho    | odology                           | 83 |

|   |     | 5.3.1    | MEMS Translation Layer            | 84 |

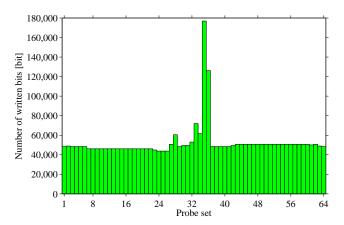

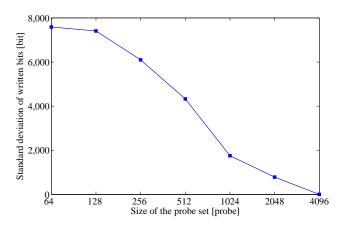

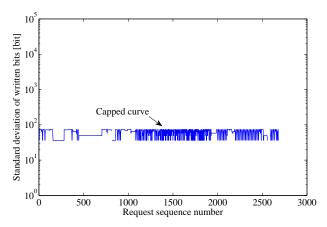

|   |     | 5.3.2    | Standard Deviation                | 85 |

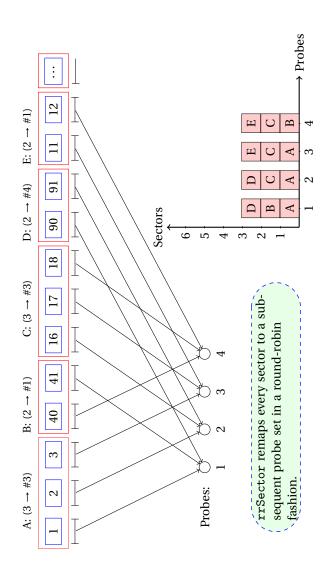

|   | 5.4 |          | ector-Based Round-Robin Policy    | 86 |

|   | 5.5 |          | oldest-Probe Policy               | 89 |

|   | 5.6 |          | arrier-Based Policy               | 92 |

|   | 5.7 |          | arison                            | 95 |

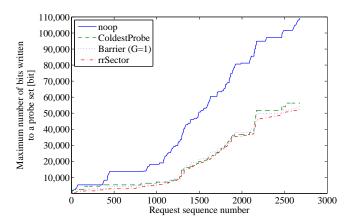

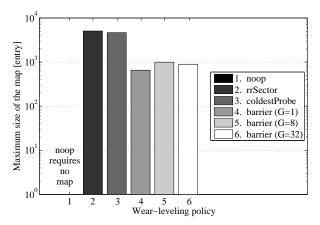

|   |     | 571      | Davica Lifetima                   | 95 |

|   |            | 5.7.2 Timing Performance and Energy-Efficiency | 96  |  |  |

|---|------------|------------------------------------------------|-----|--|--|

|   |            | 5.7.3 Storage Requirement                      | 98  |  |  |

|   |            | 5.7.4 Wear Leveling and Parallelism            | 98  |  |  |

|   |            | 5.7.5 MEMS Design Trade-offs                   | 100 |  |  |

|   | 5.8        | Wear-Leveling in Flash Memory                  | 102 |  |  |

|   | 5.9        | Summary                                        | 104 |  |  |

| 6 | Сар        | acity-Modest Applications                      | 105 |  |  |

|   | 6.1        | Methodology                                    | 105 |  |  |

|   | 6.2        | Mixed-Media Environments                       | 106 |  |  |

|   |            | 6.2.1 Configurations of the Data Layout        | 106 |  |  |

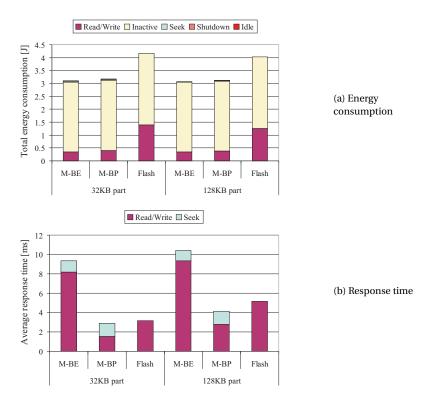

|   |            | 6.2.2 Results                                  | 108 |  |  |

|   | 6.3        | Streaming Environments                         | 109 |  |  |

|   |            | 6.3.1 Configurations of the Data Layout        | 109 |  |  |

|   |            | 6.3.2 Results                                  | 111 |  |  |

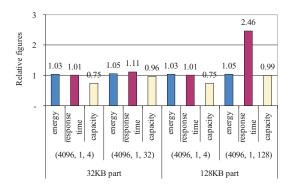

|   | 6.4        | Enhancing MEMS-Based Storage Devices           | 113 |  |  |

|   | 6.5        | Configuring for Streaming Applications         | 114 |  |  |

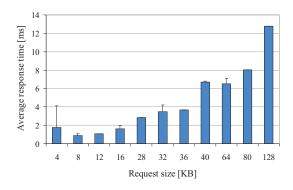

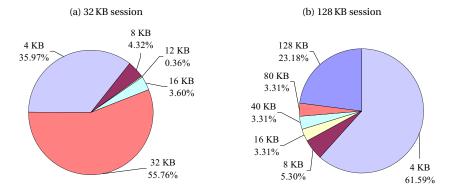

|   |            | 6.5.1 Bimodality of Request Size               | 115 |  |  |

|   |            | 6.5.2 Aggressive Prefetching                   | 116 |  |  |

|   |            | 6.5.3 Exploiting the Bimodality                | 118 |  |  |

|   | 6.6        | Summary                                        | 120 |  |  |

| 7 | Cap        | Capacity-Demanding Applications                |     |  |  |

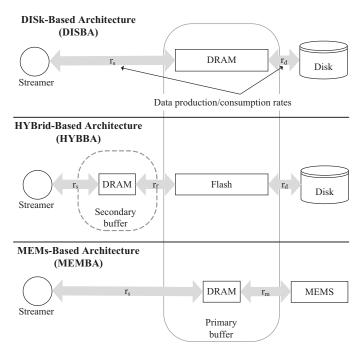

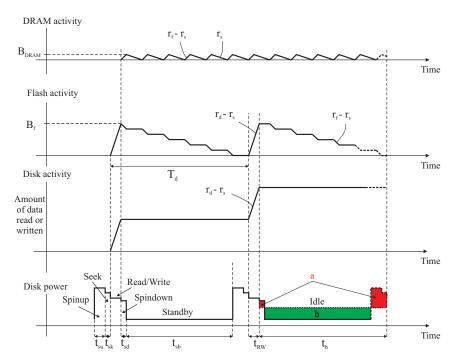

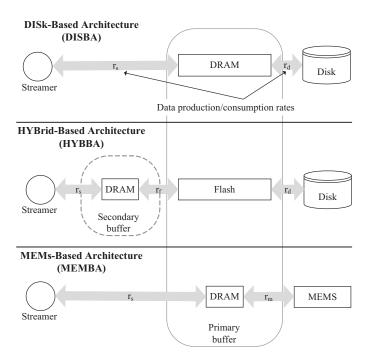

|   | 7.1        | The DISBA Architecture                         | 121 |  |  |

|   | 7.2        | The HYBBA and MEMBA Architectures              | 122 |  |  |

|   | 7.3        | Traffic Shaping                                | 124 |  |  |

|   | 7.4        | Methodology                                    | 125 |  |  |

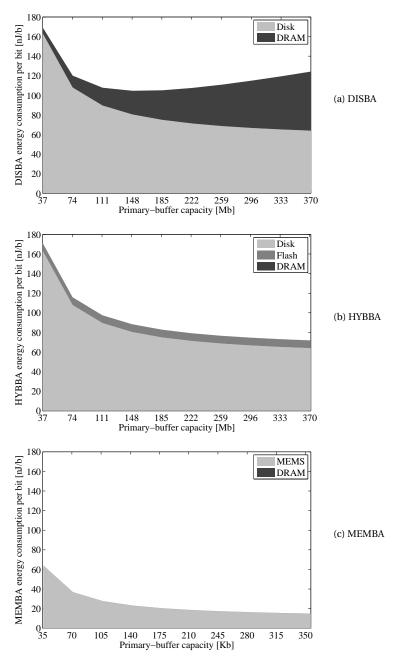

|   | 7.5        | Comparison                                     | 127 |  |  |

|   |            | 7.5.1 Buffer Capacities                        | 127 |  |  |

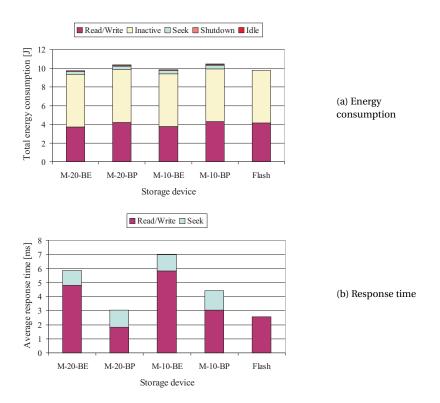

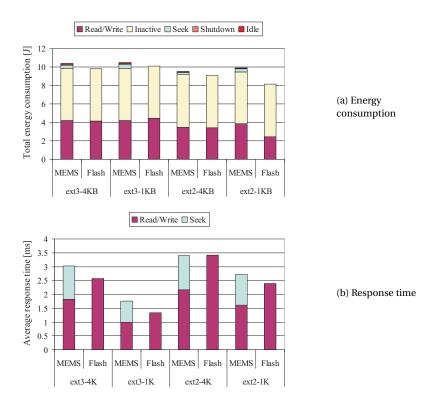

|   |            | 7.5.2 Energy Consumption                       | 127 |  |  |

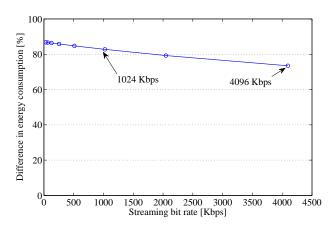

|   | 7.6        | Energy-Efficiency of MEMBA                     | 129 |  |  |

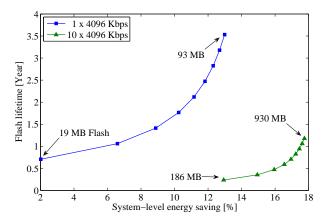

|   |            | 7.6.1 Streaming Demand                         | 129 |  |  |

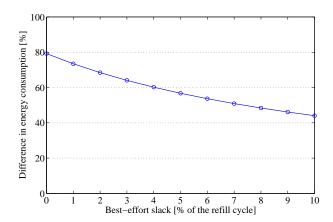

|   |            | 7.6.2 Best-Effort Demand                       | 131 |  |  |

|   | 7.7        | Reliability Study                              | 132 |  |  |

|   |            | 7.7.1 HYBBA                                    | 132 |  |  |

|   |            | 7.7.2 MEMBA                                    | 134 |  |  |

|   | 7.8        | Summary                                        | 135 |  |  |

| 8 | Con        |                                                | 137 |  |  |

|   | 8.1        | System-Level Conclusions                       | 139 |  |  |

|   |            |                                                |     |  |  |

|   | 8.2        | Architecture-Level Conclusions                 | 140 |  |  |

|   | 8.2<br>8.3 |                                                |     |  |  |

| Lis | st of A | cronyms                               | 147 |  |  |

|-----|---------|---------------------------------------|-----|--|--|

| Re  | feree   | d Publications by the Author          | 149 |  |  |

| Lis | st of P | ublications                           | 151 |  |  |

| A   | Exce    | erpts from Collected Traces           |     |  |  |

|     | A.1     | I/O Trace                             | 159 |  |  |

|     | A.2     | Power Trace                           | 159 |  |  |

|     | A.3     | Control Log                           | 160 |  |  |

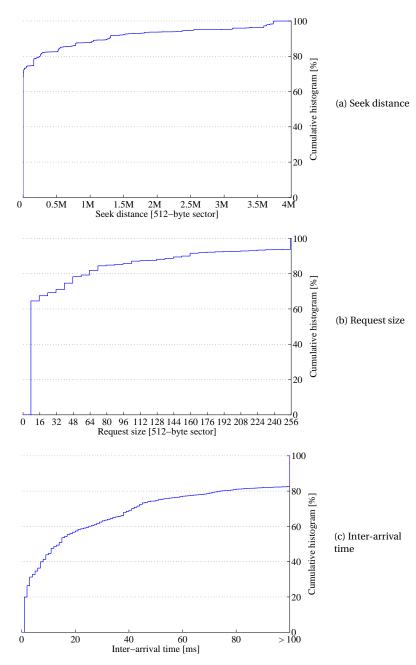

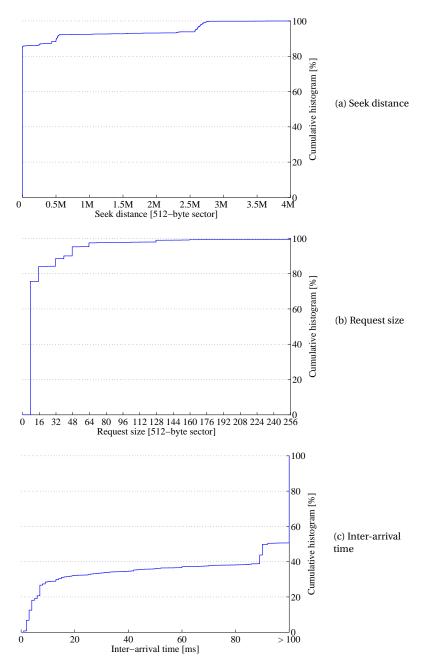

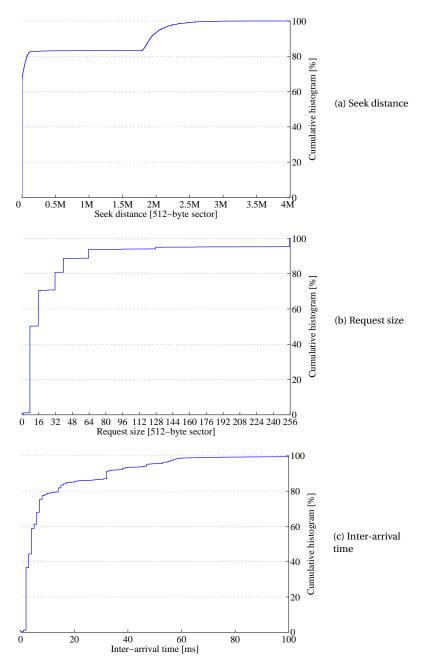

|     | A.4     | Statistics of the I/O Traces          | 161 |  |  |

| В   | Mod     | eling Two Shutdown Policies           | 167 |  |  |

|     | B.1     | Modeling                              | 167 |  |  |

|     | B.2     | The Energy-Efficient Policy           | 168 |  |  |

|     |         | B.2.1 Motion along $X$                | 169 |  |  |

|     |         | B.2.2 Motion along $Y$                | 171 |  |  |

|     | B.3     | The Performance-Efficient Policy      | 172 |  |  |

|     |         | B.3.1 Shutdown time and energy        | 173 |  |  |

|     | B.4     | Implementation in DiskSim             | 174 |  |  |

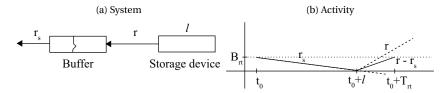

| C   | Mod     | eling Streaming Architectures         | 175 |  |  |

|     | C.1     | Energy Components                     | 175 |  |  |

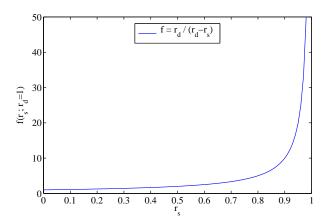

|     | C.2     | Minimizing Energy                     | 176 |  |  |

|     | C.3     | Buffer Capacities                     | 178 |  |  |

|     |         | C.3.1 The Real-Time Buffer Capacity   | 178 |  |  |

|     |         | C.3.2 The Primary Buffer Capacity     | 180 |  |  |

|     |         | C.3.3 The Secondary Buffer Capacity   | 181 |  |  |

|     | C.4     | Energy Consumption                    | 182 |  |  |

|     |         | C.4.1 Disk Energy Consumption         | 182 |  |  |

|     |         | C.4.2 Flash Energy Consumption        | 182 |  |  |

|     |         | C.4.3 DRAM Energy Consumption         | 183 |  |  |

|     | C.5     | Servicing Best-Effort Requests        | 184 |  |  |

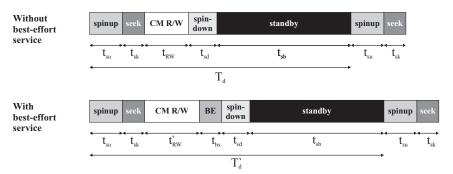

|     |         | <b></b>                               | 184 |  |  |

|     |         | C.5.2 Modeling the Best-Effort Demand | 185 |  |  |

|     |         |                                       |     |  |  |

# CHAPTER

#### INTRODUCTION

Man has recorded data for a very long time. Our ancestors carved their messages on tablets made of stone and wood. Stone and wood are durable media! It is no wonder why inscriptions carved several millennia ago are still readable today — but are not necessarily interpretable.

The digital era revolutionized the way how data are recorded. Several materials have been discovered that allow to record a huge amount of data on a small area. Yet, physicists are still pushing the envelope to achieve higher storage capacities with existing techniques as well as to innovate new storage technologies; the recently discovered Memristor [1] is just an example.

In the digital era, the amount of data a person stores has multiplied significantly. According to research companies, such as  $IDC^1$ , the overall demand for storage capacity is growing annually by about 30% - 60%. People keep track of their personal data for every event in their life. Further, laws, such as the US Sarbanes-Oxley Act of 2002 (SOX) [2] and the EU data retention directive [3], stipulate that an organization must retain its records for long periods of time.

#### 1.1 Green and High-Density Storage

The digital era coincides with an era of increasing concerns about energy conservation. Our source of energy, namely fossil fuel, is limited. Sustainable energy sources are good alternatives, but they should be used wisely.

$<sup>^{\</sup>mathrm{l}}$  http://www.idc.com

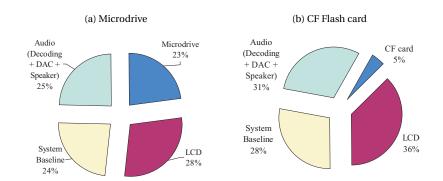

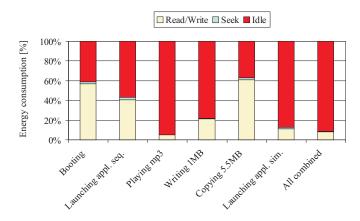

Figure 1.1: Energy breakdown of an HP iPAQ PDA measured in our laboratory when streaming at 192 Kbps from a Microdrive and a Flash card

Energy efficiency is an important design issue in a mobile computer system, since a battery has a limited capacity. Energy efficiency extends the time period during which a system is operational. Likewise, in data centers, energy efficiency reduces the direct costs, such as the energy consumption by a computer system itself, as well as indirect costs, such as cooling [4]. This is beneficial for economical and scaling reasons, since the capacity of data centers is mainly limited by their power demands [5].

The two most widely used non-volatile storage technologies to date are the Disk drive and Flash memory. A large proportion of the energy of contemporary computer systems is due to energy consumption of the inexpensive Disk drive. The more energy-efficient Flash memory is up to ten times more expensive than the Disk drive. The call for energy conservation and the demand for large storage capacities require *inexpensive green* storage systems.

#### 1.1.1 Current Storage Technologies

The Disk drive has been around for more than 50 years serving as secondary storage in computer systems. The Disk drive is inexpensive. The initial price (or cost) of a Disk drive is 0.30 - 0.80 \$/GB. Because of its mechanical nature, the Disk drive consumes a large amount of energy. Figure 1.1a shows that the smallest disk drive, the Microdrive, consumes about a quarter of the total energy consumed by a mobile computer system. The Disk drive has high endurance and can be written approximately  $10^{12}$  times.

It is predicted that the areal density of the Disk drive will continue to grow by about 40% every year, whereas the linear density (i.e., track and bit density) grows by about 15%. As a result, the bandwidth is likely to improve also by 15%, but the access time (i.e., the latency) will hardly see any improvement

(about 5% per year if any). The cost per gigabyte is expected to drop at a rate of approximately 40% per year. With respect to energy consumption, the Disk drive is expected to make little improvement [6].

Although it has already been introduced in the early eighties, Flash memory has only gained popularity in the past few years as its cost has dropped significantly. Flash memory is still more expensive than the Disk drive and costs 2.5-10.0 \$/GB. Flash memory is, however, more energy efficient than the Disk drive, since it has no mechanical parts. Figure 1.1b shows that a Flash card consumes about 5% of the total energy consumed by a computer system. Flash provides orders of magnitude shorter access time than the Disk drive. A Flash cell can be written  $10^4-10^6$  times, which is much less often than a disk.

Storage density of Flash is expected to grow as the technology node decreases, following Moore's law, and the number of bits per cell increases. Flash memory faces some challenges. Flash price should further decrease in order to provide competitive storage systems. The cost of a Flash-based storage system depends largely on the performance requirement, which determines the controller quality, the number of Flash chips, and the amount of buffering required. Flash endurance drops significantly when the Flash cell shrinks. Designers envisage that Flash memory will face significant challenges at technology nodes below 30 nm [7, 8], which has consequences for the endurance and retention of Flash<sup>2</sup>.

#### 1.1.2 MEMS-Based Storage Technology

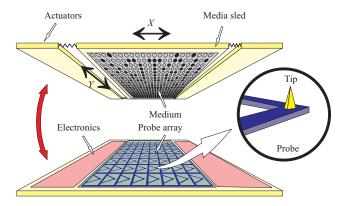

MEMS-based storage is a new technology that has been proposed in the late nineties. MEMS-based storage promises inexpensive green high-density storage systems. The technology has emerged from Scanning Probe Microscopy (SPM), where a surface is scanned and manipulated at the atomic level. This storage technology is based on Micro-Electro-Mechanical Systems (MEMS). A MEMS-based storage device consists of two separate layers facing each other as shown in Figure 1.2. The moving layer carries the storage medium, which records data. MEMS-based storage devices employ high-density recording techniques that can achieve bit dimensions down to  $1.5 \times 1.7 \, \mathrm{nm}^2$  [9]. The stationary layer is an array of thousands of read/write probes (or heads). IBM has prototyped a MEMS-based storage device with 4096 probes on an area of 41 mm². We describe MEMS-based storage in more detail in Section 2.1.

With respect to cost, MEMS-based storage devices have potentially low cost for three primary reasons. Firstly, they can be manufactured using the well established batch MEMS fabrication techniques [10]. Secondly, MEMS-based storage devices can be manufactured using micron-scale fabrication plants, whose equipment were installed ten years ago. The equipment of these

<sup>&</sup>lt;sup>2</sup> Jan van Houdt from IMEC discussed Flash challenges in his presentation at the IMST (Innovative Mass Storage Technologies) event in November 2008.

Figure 1.2: A three-dimensional sketch of a MEMS-based storage device

plants have passed their break-even point [11], avoiding the need to build dedicated fabrication plants, unlike for Flash. Thirdly, these plants can be used to produce future generations of MEMS-based storage devices, since MEMS poses no requirements on the lithography when increasing the density [11].

With respect to energy consumption, MEMS-based storage devices have a mechanical nature and therefore consume more energy than Flash and have inferior response time. Nonetheless, exploiting its unique characteristics, we make the case in this dissertation that MEMS-based storage can be used/configured to be competitive with Flash memory.

#### 1.1.3 Requirements for MEMS-Based Storage

It is generally expected that the per-bit cost of storage will drive the memory market for decades to come [6], and thus the success of a new storage technology depends mainly on its per-bit cost. Additionally, a new storage technology should at least be equivalent to existing technologies with respect to timing performance, and energy-efficiency.

For example, (NAND) Flash memory replaced the Microdrive in handheld gadgets as soon as the cost of Flash dropped below that of the Microdrive. Flash could not make it before the price dropped, despite the fact that Flash has shorter response time, consumes less energy, and has better shock resistance. Another example is the Flash-based Solid-State Disk (SSD), which is not yet widely used in mobile computers. This is because the SSD is more expensive than the Hard Disk Drive (HDD), even through the SSD outperforms the HDD on other accounts.

We believe that MEMS-based storage can find its way to the deployment stage, *if and only if* it offers lower per-bit cost than Flash memory, and is, at least, as performance- and energy-efficient. Other factors, such as long reten-

tion time, high endurance, are relevant too. This dissertation offers several optimizations that enhance the energy-efficiency, timing performance, and lifetime of MEMS-based storage devices to the level where serious deployment of MEMS-based storage could be realized. We offer a technique to increase the retained capacity of a MEMS-based storage device after formatting. Nonetheless, the per-bit cost of MEMS-based storage technology is mainly in the hand of the device designers. Innovative recording techniques are required that enable high storage densities by shrinking the cell size or storing multiple levels per cell.

#### 1.2 Research Statement

Our investigation of MEMS-based storage technology starts from the following hypothesis:

#### Hypothesis

Given its properties, a MEMS-based storage device can deliver appropriate quality of service as a non-volatile secondary-storage device in mobile computer systems.

We validate this hypothesis in the *context of mobile computer systems* (see Chapter 1.3). The validation considers a range of aspects for meaningful results.

Investigating MEMS-based storage as secondary storage includes optimizing the technology, so that it serves its task while delivering the best quality of service. Integrating MEMS-based storage raises the question of how it compares to existing technologies. The fact that MEMS-based storage technology is currently under development provides us with an opportunity to influence the design of the architecture and its components. Our research questions are:

#### **Research Questions**

- **Q1:** How can a MEMS-based storage device deliver appropriate quality of service: high energy-efficiency, high timing performance, large capacity, and long lifetime?

- **Q2:** How do MEMS-based storage devices compare to current storage devices composed out of Flash memory and the Disk drive?

- **Q3:** What are the components of a MEMS-based storage device that determine its quality of service?

#### 1.3 The A4 Project

The work in this dissertation is carried out in the context of the A4 project: **Adaptive non-volatile storAge for Adaptive Applications**. The A4 project is a joint research effort between the Electrical Engineering Department and the Computer Science Department at the University of Twente.

The basic idea of the A4 project is that adaptivity of the storage device meets with adaptivity of the application (and vice versa) for energy efficiency. One example of how adaptivity can save energy is that a MEMS-based storage device switches off some of its read/write probes that are not used for accessing the data requested by the application.

The A4 project targets mobile environments, which have stringent constraints on energy consumption, form factor, and shock resistance. *The focus of the project is on the integration of MEMS-based storage devices in mobile computer systems.* The study encompasses two parts, one at the system level and the other at the device level.

At the system level, the A4 project investigates various types of policy that enhance four aspects of a MEMS-based storage device: energy efficiency, timing performance, effective capacity, and lifetime. At the device level, on the other hand, various actuation techniques are investigated to enhance (some of) the previous aspects. The two parts complement and feed results to each other as shown in this dissertation.

#### 1.4 Contributions

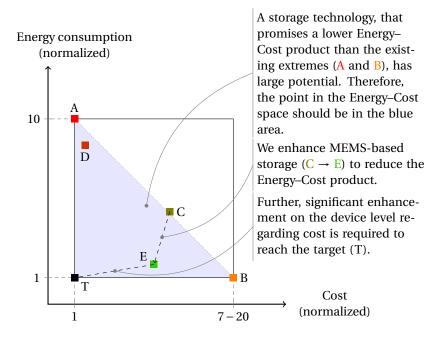

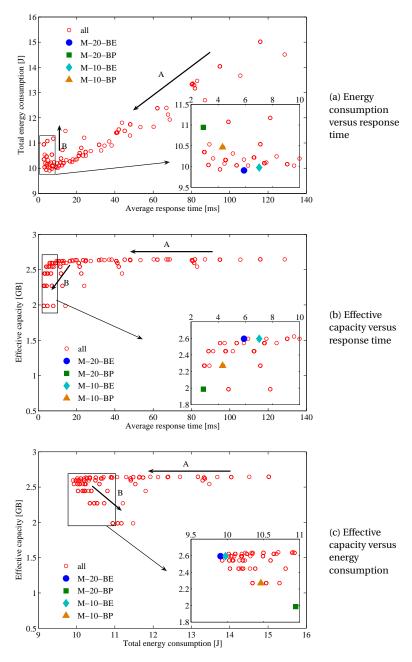

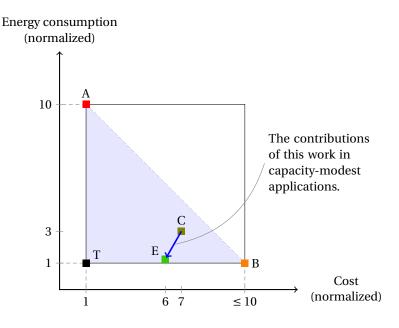

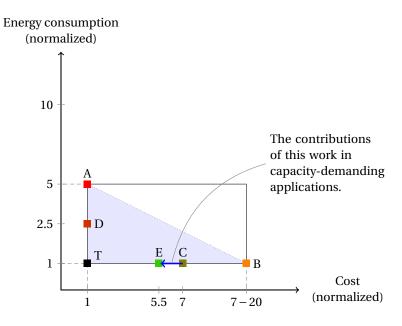

Figure 1.3 places existing storage technologies in an Energy–Cost space. The figure shows the Disk drive (point A) and Flash memory (point B) as the baseline from cost and energy perspectives, respectively. Figure 1.3 also presents the target technology (T) that offers inexpensive storage like the Disk drive and energy-efficient storage like Flash memory.

In a nutshell, our main contribution to MEMS-based storage is to reduce the energy consumption and reduce the per-bit cost by going from point C to point E in the Energy–Cost space. We also investigate the marriage between the Disk drive (A) and Flash memory (B) to construct Hybrid storage (D). We compare MEMS-based storage to Flash memory and to Hybrid storage.

Answering the three research questions, in the following, we summarize our contributions and mark the main ones with an asterisk:

**Understanding** We carefully study MEMS-based storage and investigate its unique characteristics. We survey the literature on the available designs of MEMS-based storage.

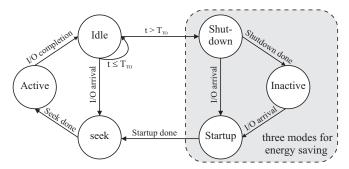

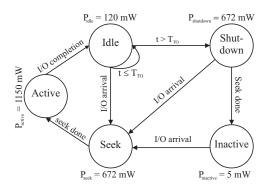

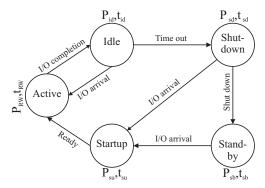

**Analyzing** The study of the characteristics results in identifying the operation modes of a MEMS-based storage device in the form of a Power State

A: Disk B: Flash C: MEMS D: Disk-Flash E: Optimized MEMS T: Target

Figure 1.3: A visualization of the relative position of each of the addressed storage technologies with respect to the per-bit cost and the per-bit access energy consumption. The Disk drive (A) and Flash memory (B) represent the baseline, respectively. The target storage technology (T) for mobile computer systems has the cost of the Disk drive, and is as energy-efficient as Flash memory. A non-optimized MEMS-based storage (C) is approximately seven times as expensive as the Disk drive, and sits approximately halfway in the range of the energy consumption. We devise enhancement policies for MEMS-based storage (E), so that it becomes competitive with Flash memory with respect to energy consumption. Further, we provide a technique to format MEMS-based storage, whereby most of its physical capacity is retained, so that it becomes less expensive. Nonetheless, device level enhancements are still needed to bring MEMS-based storage that last and crucial step toward the target (T). Current marriage between the Disk drive and the Flash memory (D) promises a greener and less expensive system than the Disk drive or the Flash memory alone. Note that the respective cost and energy consumption of the technologies changes from one environment to another (i.e., streaming and best effort), and from one storage system to another; and also changes over the time. This change reflects on the dimensions of the rectangle. We revisit the figure in Section 8.2 to reposition the technologies based on our results for capacitymodest and capacity-demanding applications.

- Machine (PSM). The operation modes allow us to optimize a MEMS-based storage device systematically for good quality of service.

- **Modeling** In a joint study with the device designers, we focus on the prototyped IBM MEMS device. We construct a model that approximates the IBM MEMS device, which we use throughout our simulation experiments. The model can be used by device researchers to test possible designs of various components of a MEMS-based storage device.

- Optimizing\* We optimize for four design targets of MEMS-based storage devices: energy consumption, response time, capacity, and lifetime. Our optimization transitions MEMS-based storage from point C to point E in the Energy–Cost space, see Figure 1.3. We offer four types of policy: a power management policy, a shutdown policy, a data-layout policy, and a wear-leveling policy. Each of the policies addresses one or more of the design targets as follows:

- **Energy** Power management transitions the device from the idle mode into the inactive mode, where the shutdown policy exploits the unique architecture of the device to shut it down in an energy-efficient manner. The data-layout policy stripes sectors across the probes, so that data are accessed efficiently.

- **Performance** We show that the response time of the device decreases if immediate shutdown decisions are avoided. We propose two shutdown policies that improve the performance for random and sequential workloads, respectively. The data-layout policy reduces the access time of requests by increasing probe utilization.

- **Capacity** Our optimization for the capacity is addressed by the datalayout policy, which strives at reducing storage overhead. We show that by exploiting knowledge of the expected workload the device can be formatted with large sectors, so that the overhead reduces and most of the physical capacity is retained.

- **Lifetime** We propose three light-weight wear-leveling policies that distribute write requests across probes, thereby avoiding the untimely demise of probes. These policies do not require complicated computations, and differ in the device lifetime they achieve versus the influence on the timing performance and energy-efficiency.

- **Configuring** Investigating the devised policies under realistic workloads, we come up with design rules for each type of policy. The design rules assist the designers of MEMS-based storage devices in implementing informed configurations.

- Integrating\* Employing a MEMS-based storage device as secondary storage has a consequence for the amount of main memory required. For predominately streaming environments, we study the influence of aggressive prefetching on the configuration of MEMS-based storage devices which has consequences for the energy efficiency and the capacity.

Comparing\* We study the response time and energy consumption of MEMS-based storage devices in two different environments: pure streaming, and mixed-media (i.e., a realistic mix of best effort and streaming applications). In both case studies, we compare MEMS-based storage with Flash memory. We also investigate a Disk–Flash Hybrid technology, and compare with MEMS-based storage.

**Designing\*** Integrating MEMS-based storage devices in the storage hierarchy, we identify potential points of enhancement on the device level. We provide device researchers with these recommendations, so that research on the device level can be oriented purposefully.

#### 1.5 Organization of the Thesis

Given the broad scope of the work (from application to device), Figure 1.4 offers a guide to reading each of our contributions separately. The content of the chapters can be summarized as follows.

Chapter 2 discusses the underlying technologies that enable MEMS-based storage. It also addresses complementary storage technologies, such as Flash memory. We detail the characteristics of MEMS-based storage devices, and detail our contributions to the existing system work on MEMS-based storage.

Chapter 3 presents the methodology adopted throughout the experiments of this work. We describe the setup, which we use to measure energy consumption of Flash memory, and to collect I/O traces. We present our MEMS model and discuss the characteristics of the traces we use for simulation. The modeling part of this chapter is joint work [Khatib: 7] with the Electrical Engineering Department of the University of Twente.

Chapter 4 defines the operation modes of a MEMS-based storage device. It presents three types of policy: power management, shutdown, and data layout. These policies are introduced to optimize for the energy consumption, timing performance, and capacity. This chapter subsumes four publications [Khatib: 2, 3, 5, 8]; the latter is joint work with the Storage Systems Research Center (SSRC) at the University of California at Santa Cruz in the USA.

Chapter 5 follows up on optimizing MEMS-based storage devices by tackling the challenge of uneven probe wear. It studies the influence of wear leveling on the timing performance and energy-efficiency. We propose three policies to extend the lifetime of MEMS-based storage devices. The policies have different trade-offs between lifetime, performance, and energy-efficiency.

Chapter 6 presents two case studies, where a MEMS-based storage device serves as secondary storage in capacity-modest mobile systems, such as PDAs. Simulation results of a MEMS-based storage device are compared with empirical measurements of a Flash card. We also present a quick and effective method to configure MEMS-based storage devices for streaming environments. The chapter is based in part on a publication [Khatib: 3].

Figure 1.4: The contributions of this work to MEMS-based storage broken down into their respective chapters

Chapter 7 contributes to enhancing the energy efficiency of the storage hierarchy in capacity-demanding streaming systems, such as portable video players. We propose two approaches: (1) interposing Flash between the Disk drive and the DRAM, and (2) replacing the Disk drive with MEMS-based storage. We provide an analytical study that discusses the energy saving of the two approaches. This chapter subsumes two publications [Khatib: 1, 4].

Chapter 8 summarizes, gives a concise list of recommendations for the design on the device level, and concludes with a prospect of future work.

#### BACKGROUND AND RELATED WORK

This chapter introduces MEMS-based storage, and studies its characteristics. We present the proposed design models of MEMS-based storage and their common architecture. Two current competing storage technologies are also discussed along with their characteristics. Last, we discuss the work available on MEMS-based storage in the literature, and position our contributions.

#### 2.1 MEMS-Based Storage

This dissertation investigates a recent storage technology, based on Micro-Electro-Mechanical Systems (MEMS), called MEMS-based storage. The technology is also called Probe-based storage particularly by electrical engineers; we use the term MEMS-based storage throughout the dissertation, since it is mainly used by system people, to whom this dissertation is mainly targeted. In fact, either term is a shorthand of "scanning-parallel-probe MEMS-based data storage", which states that we work on a storage technology that employs a large number of probes in parallel to access data from a storage medium. Components of the device are fabricated and integrated into one device using MEMS techniques.

#### 2.1.1 Enabling Technologies

MEMS-based storage would not have been possible without the advent of two significant technologies. The first technology enables ultrahigh storage den-

sity, called probe recording. The second technology enables the realization of micro-machined storage systems. We explain them in the following sections. In addition to the two technologies, we present the proposed recording techniques.

#### **Atomic Force Microscopy (AFM)**

MEMS-based storage technology exploits a technique similar to Atomic Force Microscopy (AFM) to read and write bits. AFM deploys probes of nanometersharp tips to image, measure, and manipulate matters of a surface down to the atomic level. AFM was invented by Gerd Binnig, Calvin F. Quate and Christoph Gerber in 1986 [12]. In AFM, when the tip of a probe is brought into proximity of a surface, a force between the tip and the sample leads to a deflection of the cantilever of the probe. The deflection can be measured in several ways, such as using a laser spot reflected from the top of the cantilever into an array of photodiodes. Storing the measured deflections for a full scan of a surface results in a 3-dimensional profile of the surface. AFM has a high resolution in the order of fractions of a nanometer.

Contribution to MEMS-based storage The invention of AFM and its precursor Scanning Tunneling Microscopy (STM) [13] has opened a branch of microscopy, called Scanning Probe Microscopy (SPM). SPM forms an image of a surface using a physical probe to scan a specimen. SPM has inspired researchers to propose probe-based storage. The basic idea is that the ability to manipulate and sense matters of a surface enables the data storage. If after manipulation the change in matters during a certain time period is insignificant, non-volatile storage can be established.

#### **Micro-Electro-Mechanical Systems (MEMS)**

The second technology is Micro-Electro-Mechanical Systems (MEMS), which integrates mechanical elements, sensors, actuators, and electronics on a common silicon substrate. MEMS can be fabricated using modified semiconductor fabrication techniques. These techniques selectively etch away parts of a silicon (or other material) wafer and add layers to form the mechanical or electromechanical system. The research field of MEMS aspires to realize a complete computer system on a single chip [14]; researchers aspire to integrate the processor, the memory system, and a MEMS-based storage device into one chip in the future.

MEMS have an expanding range of applications [15]. Accelerometers and pressure sensors top these applications at present [16]. These sensors are deployed in automotive, medical, and consumer products. Radio-Frequency Micro-Electro-Mechanical Systems (RF-MEMS) are used to produce digital capacitors that can be tuned to different bands at run time [17]. Also, MEMS-

based gyroscopes are used to park the head in the disk drive in the case of a sudden fall. Another application area is probe storage based on MEMS, which this dissertation contributes to.

**Contribution to MEMS-based storage** MEMS technology provides a miniaturized movement mechanism that is needed to scan and manipulate a surface. The storage medium is mounted on a sled, which is brought into position by micron-scale actuators [18]. As a result, the sled moves with respect to the probes, which read/write data. MEMS actuators differ in, among others, traveling speed and power dissipation. Therefore, the type of actuators used influences the timing performance and the energy consumption of a MEMS-based storage device.

#### **Data Recording Techniques**

In addition to the previous two technologies, that enable the read/write and actuation in MEMS-based storage, techniques for data recording are under investigation. Several recording techniques have been proposed for probebased storage. Such recording techniques are magnetic-orientation switching [14, 19], topographic transformation [20], ferroelectric polarization [21], charge storage [22], and phase change [23].

#### 2.1.2 Designs

Several design concepts for MEMS-based storage have been proposed and investigated. We discuss the Micro Scanning Probe Array Memory ( $\mu$ SPAM) concept proposed by researchers at the University of Twente, and the most advanced prototyped concept from IBM, namely the Millipede concept.

#### The µSPAM Concept

A large project has been established at the University of Twente to research MEMS-based storage:  $\mu$ SPAM [24]. The project represents a design concept of MEMS-based storage as envisioned by Twente researchers. The  $\mu$ SPAM project encompasses several groups: MEMS fabrication [25], probe development [26], tip-sample investigation [27], control [18], magnetic-medium development [28], and computer-system integration, which is the topic of this dissertation.

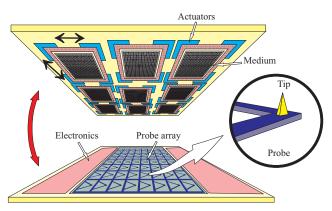

A  $\mu$ SPAM device has several storage media that move independently by electrostatic MEMS actuators, see Figure 2.1 for illustration. Each medium is accessible by a specific subset of the probe array. All storage media use a patterned magnetic technique, where one dot represents a bit. The patterned magnetic technique is under development at the Institute for Nanotechnology

Figure 2.1: A three-dimensional conceptual view of the Micro Scanning Probe Array Memory (µSPAM) investigated at the University of Twente.

at the University of Twente (MESA+). The targeted main characteristics of the  $\mu\text{SPAM}$  device are presented in Table 2.1.

A  $\mu\text{SPAM}$  device employs magnetic probes. To write a bit, a probe comes into proximity of the magnetic medium. Due to the magnetic field of the probe, in combination with an external background field, the orientation of a magnetic dot is changed. The magnetization is out of the plane of the medium. The orientation of a dot represents the logical value of the bit. The read-out measures the magnetic forces created by the magnetic dot.

In ultrahigh densities, that exhibit a bit pitch in the order of 25 nm, addressing and accessing a track of bits at a high speed are challenging tasks. This is because the actuators must have a lateral resolution better than 25 nm in order to address densely packed bits with high precision. Another challenge is maintaining a constant distance between the tip and the medium in the order of 10 nm [27].

From a system perspective, the existence of several independently moving sleds gives a  $\mu\text{SPAM}$  device performance and energy advantages. Sleds can be moved to different locations to access data at the same time, reducing the access time. Parallel read and write requests can be dispatched simultaneously to different sleds for service. Further, unused sleds can be shut down (i.e., halted) to save energy.

#### The Millipede Concept

IBM has been working on MEMS-based storage for a decade in a project called Millipede. The Millipede project brought MEMS-based storage out of its infancy by realizing a prototype of a full MEMS-based storage device, which exhibits a storage density of  $840\,\mathrm{Gb/in^2}$  and a bit error rate of  $10^{-4}$  [29]. IBM has

| Characteristic               | μSPAM                   | IBM MEMS                    | Unit               |

|------------------------------|-------------------------|-----------------------------|--------------------|

| Dimensions                   | $15 \times 15 \times 2$ | $9.6 \times 9.6 \times 0.8$ | $mm^3$             |

| Total capacity               | 20                      | 7.63                        | GB                 |

| Density                      | 1000                    | 840                         | Gb/in <sup>2</sup> |

| Number of probes             | $128 \times 128$        | $64 \times 64$              | probes             |

| Per-probe data rate          | 10                      | 40                          | Kb/s               |

| Maximum data rate            | 20                      | 20                          | MB/s               |

| Seek time                    | < 2.5                   | < 1.5                       | ms                 |

| Read/Write power dissipation | < 1                     | ≈ 1                         | W                  |

| Standby power dissipation    | $10^{-6}$               | 0.005                       | W                  |

Table 2.1: Targeted characteristics of the  $\mu$ SPAM device and present characteristics of the prototype of the IBM MEMS device

recently demonstrated storage densities up to 4 Tb/in<sup>2</sup> [30].

Unlike a  $\mu$ SPAM device, an IBM MEMS device has one storage medium. The media sled is suspended across a probe array of  $64 \times 64$  probes in the latest prototype. Bits are recorded in a thin polymer film as nanometer-scale indentations. Table 2.1 lists the key characteristics of a recent prototype.

An IBM MEMS device employs thermomechanical probes. An IBM MEMS writes a bit by applying a local electrostatic force on the tip of a probe and simultaneously heating the write resistor of the probe to 400°C to soften the polymer locally. This process results in a nanometer-scale indentation, which represents a bit of value "1". During reading, a second resistor, mounted next to the tip, is heated in the range of 150–190°C. When the tip moves into an indentation the thermal conductance between the cantilever and the media increases, resulting in a lower temperature of the heater, which can be detected by measuring its electrical resistance, and used as a read-out signal. To erase bits, thermomechanical effects relax the closely surrounding area of an indentation, so that it looses its depth and thus does not represent a "1".

#### **Other Concepts**

The promising ultrahigh density of probe-based storage has drawn the attention of academia as well as industry. In addition to the  $\mu\text{SPAM}$  and the Millipede concepts, several other concepts for MEMS-based storage have been proposed.

Carnegie Mellon University has proposed a single magnetic medium actuated by electrostatic actuators, called MEMStore. MEMStore has been intensively studied by system researchers and compared to disk drives. We discuss the work on MEMStore in Sections 2.3 and 3.2.4. Beside IBM, several indus-

Figure 2.2: A three-dimensional conceptual view of a single-sled MEMS-based storage device

tries have been working on MEMS-based storage, including LG Electronics, Samsung, and Nanochip. LG Electronics proposed the Nano Data Storage System, that employs several arrays of probes for thermomechanical data storage on a polymer medium [31]. Samsung, jointly with Korean universities, is developing the Resistive Probe Storage System, that applies transistor technology to record bits on ferroelectric media [32]. Nanochip is developing a storage system to record bits on a phase-change medium. Nanochip is expecting the debut of its first product in 2010 [11].

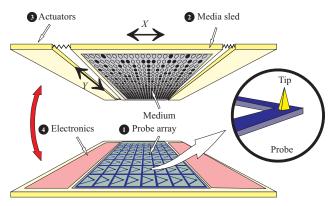

#### 2.1.3 Architecture

Several design models for MEMS-based storage have been proposed. Despite that these models employ different recording and actuation techniques, they have a common architecture. A MEMS-based storage device consists of two separate physical layers, one above the other, as shown in Figure 2.2. The top layer, the **media sled**, is suspended by springs across the bottom layer. The bottom layer is a two-dimensional array of read/write probes, the **probe array**. In addition to the storage medium and the probe array, a MEMS-based storage device has two other components, namely the **actuators** and **electronics**.

The probe array typically has several thousands of probes. The probe array is stationary and connected to the electronics. Increasing the number of parallel probes, enhances the throughput. The probe must have a nanometer-sharp tip to address a bit location on the medium with high precision. An imprecise addressing overwrites neighboring bits and thus damages data. Further, a probe tip should be durable to withstand wearing conditions for a sufficiently long lifetime.

Bits are recorded using different techniques. Such techniques are mag-

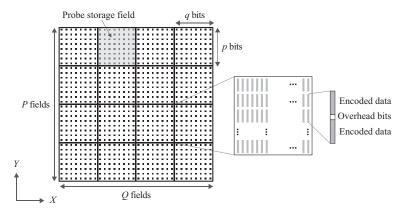

netic, phase change, and thermomechanical manipulation. The sled, which carries the storage medium, moves independently in the X, Y, and Z directions relative to the probe array. In all design models, each probe sweeps over a bounded area of the media sled, called the **probe** (**storage**) **field**. The movement along the Z direction is controlled per probe, unlike the other two directions. Consequently, seek times shorten and a relatively high (aggregate) data rate is attainable by operating many probes simultaneously.

The third main component of a MEMS-based storage device encompasses the micron-scale X, Y, and Z actuators. The media sled is attached to actuators to displace the storage medium relative to the probe array, so that data can be read from and written to the storage medium. Actuators should be able to operate at a high resolution in the sub-nanometer range to address nanometer-scale bits in ultrahigh-density storage. Since motion is necessary to access data, the actuators should allow for high access speeds at low energy consumption. Actuators can be, for example, electromagnetic as in the IBM MEMS device [29] or electrostatic [33].

The electronics is the fourth component, which is integrated with the other components. The electronics encompass the analog front-end, multiplexers, and digital components that error-correct data, control the mechanics, carry out housekeeping tasks, and interface the device to the host computer system. The interface accounts for the inactive energy, which constitutes a large fraction of the total energy, when power management is implemented.

#### 2.1.4 Characteristics

A thorough understanding of the characteristics of a new technology, including its limitations and challenges, is of paramount importance for a successful employment of the technology. This is also the case for MEMS-based storage technology. We discuss its characteristics with respect to the medium, the probes, the actuators, and the device as a whole. We label these characteristics for ease of reference later.

MEMS-based storage devices have common characteristics, which stem mainly from their common architecture as well as their basic AFM and MEMS technologies detailed previously. In the following, we lay out these characteristics and point out their consequences for the timing performance, energy consumption, capacity, and lifetime of MEMS-based storage devices.

M1: Spring-suspended sled The media sled is suspended by springs across the probe array in MEMS-based storage devices (see Figure 2.2). Unlike disk drives, which spin up the medium before the head can be positioned across it, in MEMS-based storage devices the probe is always positioned directly across the medium. Therefore, MEMS-based storage devices have no mechanical startup overhead.

M2: Light-weight sled The media sled is the only moving part in a MEMS-

- based storage device. The mass of the media sled determines the time to accelerate and decelerate the sled. Consequently, it determines the amount of power, needed to generate sufficient force for actuation, and thus influences the energy consumption.

- M3: Low per-probe data rate The data rate a probe can sustain is limited by several factors including the resonance frequency of the probe and the time to switch a bit on the medium between "0" and "1". Consequently, the per-probe data rate is inherently low; the per-probe data rate in the current prototype of the IBM MEMS device is 40 Kb/s [10]. A MEMS-based storage device employs an array of parallel probes to attain high aggregate data rates.

- **M4: Regularly spaced probes** Probes are mounted on one single substrate at equal distances from each other. In the IBM MEMS device, probes are separated by  $100 \, \mu m$  in the X and Y directions. This results in square probe fields of the same dimensions; for example a field is  $100 \, \mu m \times 100 \, \mu m$  in the IBM MEMS device. As a result, probe fields contain the same number of bits and thus have the same capacity.

- **M5: Large number of probes** The large number of probes sharing one single medium limits the sweep area of a probe to a small area on the storage medium called the probe storage field. As a result, seek times become shorter and thus the seek energy decreases.

- **M6: Nanometer-sharp probe tips** As detailed previously, AFM probes must have a sharp tip in the order of a nanometer for a precise scan, manipulation, or measurement of a surface. Such tips can pass an electrical current, make contact with the storage medium, and/or heat up, depending on the recording technique. As a result, a probe tip can loose its sharpness and/or its coating material, resulting in probe wear. As a probe is used more often, it wears faster and its lifetime becomes shorter.

- **M7: Separate** X **and** Y **actuations** A MEMS-based storage device deploys two separate pairs of actuators to move the media sled independently in the X and Y directions at the same time. As a result, the time to move the sled from one position to another, known as the seek time, is the maximum time to seek along the X and Y directions.

- **M8:** *Z* **nanopositioners** The spacing between the probe tip and the medium is dynamically maintained by nanopositioners. Because of the roughness of the medium, nanopositioners are used to maintain a nanometer-scale constant spacing, which is necessary for bit manipulation in contactless MEMS-based storage devices. Nanopositioners avoid a probe tip accidentally hitting the medium. In the IBM MEMS device, the probe makes contact with the medium only at read/write time using electrostatic force. Typically, the spacing between the tip and the medium in

the IBM MEMS device is in the order of hundreds of nanometers [29], so that accidental hits are hardly possible.

- **M9: Mechanical nature** A MEMS-based storage device has a moving media sled. To achieve high throughput, a MEMS-based storage device should move the sled as fast as possible, and should not interrupt the sled motion whenever possible. Therefore, data are laid out along one direction, conventionally taken as the *Y* direction in this work.

- M10: Ultrahigh density Ultrahigh densities of over 4 Tb/in<sup>2</sup> can be achieved with MEMS-based storage [29], resulting in large-capacity, small-form-factor devices employable almost everywhere. However, as the density increases, the time to position a probe above the center of a track of bits accurately, known as the settling time, also increases. A precise positioning is necessary for data integrity.

- M11: Error proneness Storage devices are error prone for many reasons, such as errors in the medium and probes. Therefore, a MEMS-based storage device should add error-correction bits to user data and encode them before writing to the medium [29]. Error detection and correction occur at read time. The increase in reliability clearly comes at the cost of an increase in response time and energy consumption as well as a decrease in the effective capacity.

Having explained the main topic of this dissertation, namely MEMS-based storage device, we provide next a brief discussion of Flash memory and Phase-Change memory. MEMS-based storage has to be competitive with these two technologies.

# 2.2 Complementary Storage Technologies

Several storage technologies have been proposed. These technologies are at different stages in their development course spanning from fundamental investigation to advanced development, and end in deployment. Memristor memory [1] and racetrack memory [34] are in the early fundamental stage, whereas Phase-Change Memory [35] is still in the development stage. On the other hand, MEMS-based storage is nearing deployment and Flash memory is already deployed.

# 2.2.1 Flash Memory

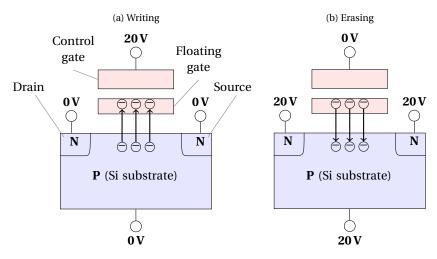

Flash was invented by Fujio Masuoka while working for Toshiba in 1980 [36]. Invention of Flash was motivated by the view that the cost per bit is the key driving factor of the memory market. Flash memory uses the same principles of operation as the byte-addressable Electrically Erasable Programable Read-Only Memory (EEPROM). The main invention of Flash memory was,

Figure 2.3: Writing (or programming) and erasing in Flash memory is achieved by tunneling between the floating gate and the substrate. Observe the different voltages applied at the terminals when writing and erasing.

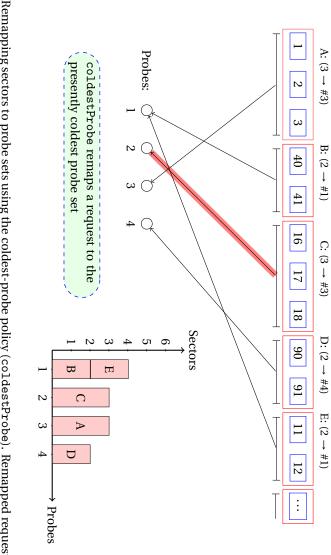

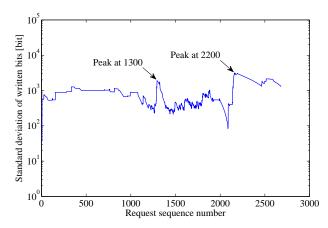

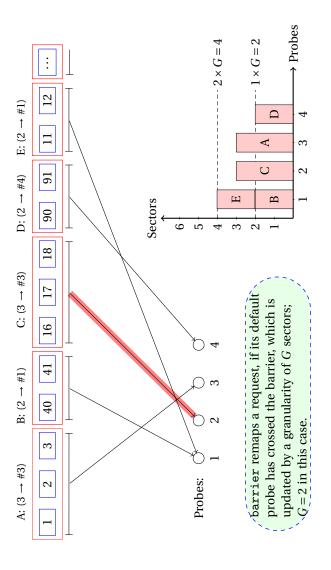

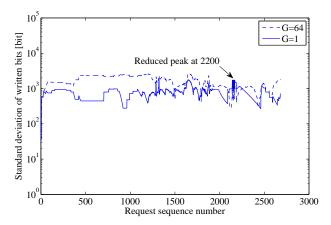

to cut on the cell area and thus its cost, one of the two transistors in the byte-addressable EEPROM cell is removed. This transistor is responsible for the erasure on a bit level. Therefore, Flash erases on larger granularity than one bit, and, back then, was called the simultaneously erasable EEPROM. The name "Flash" was suggested later in 1984, since Flash has to erase a block simultaneously, which resembles the flash of a camera.